The F018 "DMAgic" DMA controller at 0xd700. More...

#include <_dmagic.h>

Public Attributes | |

| uint8_t | addr_lsb_trigger |

| DMAgic DMA list address LSB, and trigger DMA (when written) (offset 0x00) More... | |

| uint8_t | addr_msb |

| DMA list address high byte (address bits 8 – 15) (offset 0x01) More... | |

| uint8_t | addr_bank |

| DMA list address bank (address bits 16 – 22). Writing clears $D704 (offset 0x02) More... | |

| uint8_t | enable_f018b |

| Offset 0x03, extensed fields. More... | |

| uint8_t | addr_mb |

| DMA list address mega-byte (offset 0x04) More... | |

| uint8_t | trigger_enhanced |

| Set low-order byte of DMA list address, and trigger Enhanced DMA job (offset 0x05) More... | |

| uint8_t | etrigmapd |

| Set low-order byte of DMAlistaddress and trigger EnhancedDMA job, with list in current CPU memory map (offset 0x06) More... | |

| uint8_t | unused1 [7] |

| Offset 0x07-0x0d. More... | |

| uint8_t | addr_lsb |

| DMA list address low byte (address bits 0 – 7) WITHOUT STARTING A DMA JOB (offset 0x0e) More... | |

| uint8_t | unused2 [2] |

| Offset 0x0f-0x10. More... | |

| uint8_t | auden |

| Enable Audio DMA (offset 0x11) More... | |

| uint8_t | unused3 [10] |

| Offset 0x12-0x1b. More... | |

| uint8_t | ch0rvol |

| Channel 0 right channel volume (offset 0x1c) More... | |

| uint8_t | ch1rvol |

| Channel 1 right channel volume (offset 0x1d) More... | |

| uint8_t | ch2lvol |

| Channel 2 left channel volume (offset 0x1e) More... | |

| uint8_t | ch3lvol |

| Channel 3 left channel volume (offset 0x1f) More... | |

| union { | |

| struct { | |

| struct DMAAudioChannel ch0 | |

| Audio DMA channel 0 (offset 0x20) More... | |

| struct DMAAudioChannel ch1 | |

| Audio DMA channel 1 (offset 0x30) More... | |

| struct DMAAudioChannel ch2 | |

| Audio DMA channel 2 (offset 0x40) More... | |

| struct DMAAudioChannel ch3 | |

| Audio DMA channel 3 (offset 0x50) More... | |

| } | |

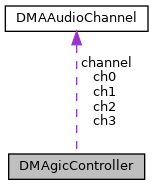

| struct DMAAudioChannel channel [4] | |

| Audio channels as an array (offset 0x20) More... | |

| }; | |

Detailed Description

The F018 "DMAgic" DMA controller at 0xd700.

Member Data Documentation

◆

| union { ... } |

◆ addr_bank

| uint8_t DMAgicController::addr_bank |

DMA list address bank (address bits 16 – 22). Writing clears $D704 (offset 0x02)

◆ addr_lsb

| uint8_t DMAgicController::addr_lsb |

DMA list address low byte (address bits 0 – 7) WITHOUT STARTING A DMA JOB (offset 0x0e)

◆ addr_lsb_trigger

| uint8_t DMAgicController::addr_lsb_trigger |

DMAgic DMA list address LSB, and trigger DMA (when written) (offset 0x00)

◆ addr_mb

| uint8_t DMAgicController::addr_mb |

DMA list address mega-byte (offset 0x04)

◆ addr_msb

| uint8_t DMAgicController::addr_msb |

DMA list address high byte (address bits 8 – 15) (offset 0x01)

◆ auden

| uint8_t DMAgicController::auden |

Enable Audio DMA (offset 0x11)

◆ ch0

| struct DMAAudioChannel DMAgicController::ch0 |

Audio DMA channel 0 (offset 0x20)

◆ ch0rvol

| uint8_t DMAgicController::ch0rvol |

Channel 0 right channel volume (offset 0x1c)

◆ ch1

| struct DMAAudioChannel DMAgicController::ch1 |

Audio DMA channel 1 (offset 0x30)

◆ ch1rvol

| uint8_t DMAgicController::ch1rvol |

Channel 1 right channel volume (offset 0x1d)

◆ ch2

| struct DMAAudioChannel DMAgicController::ch2 |

Audio DMA channel 2 (offset 0x40)

◆ ch2lvol

| uint8_t DMAgicController::ch2lvol |

Channel 2 left channel volume (offset 0x1e)

◆ ch3

| struct DMAAudioChannel DMAgicController::ch3 |

Audio DMA channel 3 (offset 0x50)

◆ ch3lvol

| uint8_t DMAgicController::ch3lvol |

Channel 3 left channel volume (offset 0x1f)

◆ channel

| struct DMAAudioChannel DMAgicController::channel[4] |

Audio channels as an array (offset 0x20)

◆ enable_f018b

| uint8_t DMAgicController::enable_f018b |

Offset 0x03, extensed fields.

◆ etrigmapd

| uint8_t DMAgicController::etrigmapd |

Set low-order byte of DMAlistaddress and trigger EnhancedDMA job, with list in current CPU memory map (offset 0x06)

◆ trigger_enhanced

| uint8_t DMAgicController::trigger_enhanced |

Set low-order byte of DMA list address, and trigger Enhanced DMA job (offset 0x05)

◆ unused1

| uint8_t DMAgicController::unused1[7] |

Offset 0x07-0x0d.

◆ unused2

| uint8_t DMAgicController::unused2[2] |

Offset 0x0f-0x10.

◆ unused3

| uint8_t DMAgicController::unused3[10] |

Offset 0x12-0x1b.

The documentation for this struct was generated from the following file:

- mega65/_dmagic.h